逻辑门

逻辑门是实现布尔函数的设备,也就是说,它对输入的一个或多个位进行逻辑操作,并给出一个位作为输出。它们是任何数字系统的基本构件。它是一个电子电路一个或多个输入,只一个输出.输入和输出之间的关系是基于某种逻辑的。因此逻辑门被命名为与门、或门、非门等。

逻辑学家、哲学家、计算机科学家、程序员、电子工程师和语言学家都对布尔函数感兴趣。它们是今天计算技术的基础。

真值表

真值表基本上是一种全面定义布尔函数的方法。它们由输入位的所有可能的排列以及对应的函数值组成。

有多少 -ary布尔函数是否存在?

域的大小 -ary Boolean函数 .

这意味着我们会 真值表中的行。因为有两种方法来填充每个的输出 可能的输入,我们有 可能的功能。

基本逻辑门

主要有三个逻辑门:或者和不.所有其他逻辑门可以表示为这些逻辑门的组合。

和

真值表

| 一个 | b | a和b |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

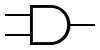

象征

或

真值表

| 一个 | b | a或b |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

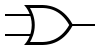

象征

不

真值表

| 一个 | 不是一个 |

| 0 | 1 |

| 1 | 0 |

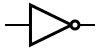

象征

通用逻辑门

虽然所有的逻辑门都可以用主逻辑门来设计,但是与非或也不可单独实现对所有主逻辑门的设计。因此,这些门被称为通用逻辑门。

与非

A and b = not (A and b)

真值表

| 一个 | b | NAND b |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

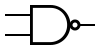

象征

也不

A nor b = not (A or b)

真值表

| 一个 | b | a和b |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

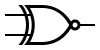

象征

派生的逻辑门

派生逻辑门是由两个或多个主逻辑门组合而成的。我们将讨论一些重要的导出逻辑门。

XOR

xor b =(a或b)和(不是(a和b))

直观上,异或是互斥的或,即A或B,但不是两者。

真值表

| 一个 | b | XOR b |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

象征

XNOR

A xor b = (A and b) or (not (A) and not (b))

真值表

| 一个 | b | XNOR b |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

象征

数字电路中的实现

逻辑门是用不同的晶体管组合而成的,它们基本上是电控开关。有两种晶体管:PNP和NPN。我们将在下面的例子中使用后者:

当一个小电流被加到NPN晶体管的“基极”上时,它允许主电流从输入端(称为“集电极”)流向输出端(称为“发射极”)。这对应于一个闭合的开关,逻辑状态为“1”。当基极上没有电流时,晶体管不再允许电流从集电极流向发射极。这对应于一个打开的开关,逻辑状态为'0'。

和

当电流作用于两个晶体管的基极时(即 ),主电流可以自由地从晶体管A'的顶部收集器流动,一直到晶体管'B'的底部发射极。如果只有两个基础中的一个“开”,则在“关闭”状态下到达晶体管时,主电流将被阻止,并且将无法流动。显然,如果两个晶体管都是“关闭”,则无电流将流动。

或

当一个小电流被施加到两个晶体管中的任何一个,或者更好的是两个晶体管上时,主电流就可以从电路的顶部自由地流到底部。只有当两个晶体管都处于“关”状态时,才没有电流流过。

不

这个特殊的栅极甚至可以用一个晶体管实现。当发射机底座(即发射机底座)没有电流时。 ),主要电流将无法流过晶体管,它的唯一出路将是通过电线 ;因此 .另一方面,当小电流施加到晶体管的基础时( ,所有的主要电流将通过它,没有电流将进入电线 ;因此 .

注意:当构建实际电路时,与门和或门非常简单,非门需要一些额外的组件来确保适当的工作条件。尽管如此,它背后的基本概念是不变的。